The 8051 microcontrollers work with 8-bit data bus. So they can

support external data memory up to 64K and external program memory of

64k at best. Collectively, 8051 microcontrollers can address 128k of

external memory.

When data and code lie in different memory blocks, then the architecture is referred as Harvard architecture. In case data and code lie in the same memory block, then the architecture is referred as Von Neumann architecture.

Von-Neumann architecture supports simple hardware. It allows the use

of a single, sequential memory. Today's processing speeds vastly outpace

memory access times, and we employ a very fast but small amount of

memory (cache) local to the processor.

Von-Neumann architecture supports simple hardware. It allows the use

of a single, sequential memory. Today's processing speeds vastly outpace

memory access times, and we employ a very fast but small amount of

memory (cache) local to the processor.

Programs needed to be loaded by an operator; the processor could not boot itself. In a Harvard architecture, there is no need to make the two memories share properties.

In the early 1980s, computer designers recommended that computers should use fewer instructions with simple constructs so that they can be executed much faster within the CPU without having to use memory. Such computers are classified as Reduced Instruction Set Computer or RISC.

When data and code lie in different memory blocks, then the architecture is referred as Harvard architecture. In case data and code lie in the same memory block, then the architecture is referred as Von Neumann architecture.

Von Neumann Architecture

The Von Neumann architecture was first proposed by a computer scientist John von Neumann. In this architecture, one data path or bus exists for both instruction and data. As a result, the CPU does one operation at a time. It either fetches an instruction from memory, or performs read/write operation on data. So an instruction fetch and a data operation cannot occur simultaneously, sharing a common bus. Von-Neumann architecture supports simple hardware. It allows the use

of a single, sequential memory. Today's processing speeds vastly outpace

memory access times, and we employ a very fast but small amount of

memory (cache) local to the processor.

Von-Neumann architecture supports simple hardware. It allows the use

of a single, sequential memory. Today's processing speeds vastly outpace

memory access times, and we employ a very fast but small amount of

memory (cache) local to the processor.Harvard Architecture

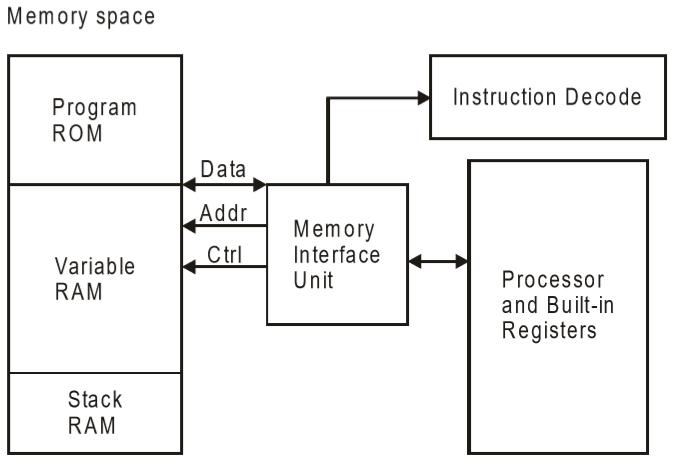

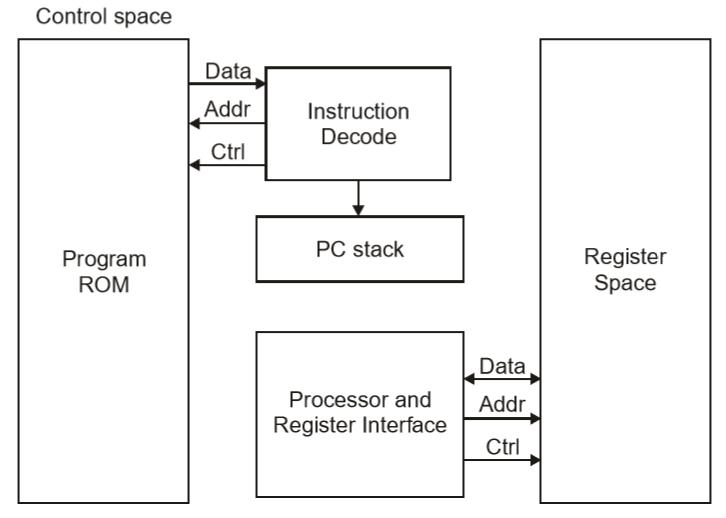

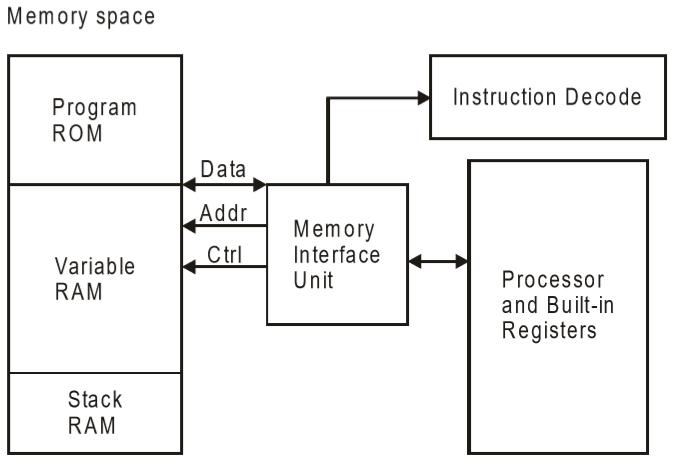

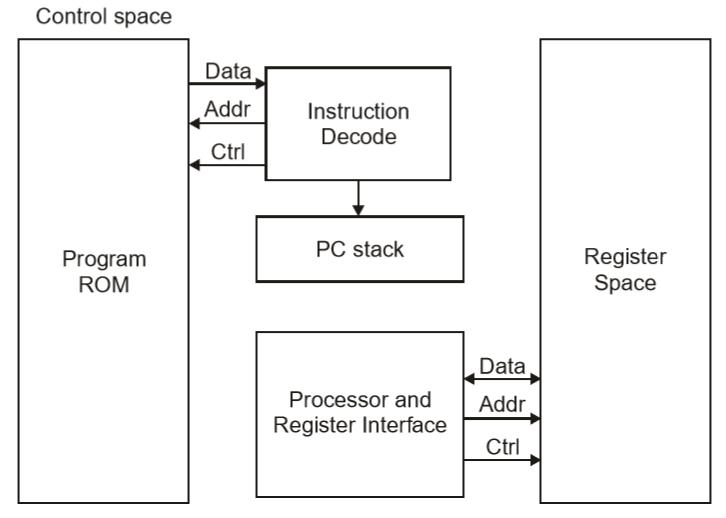

The Harvard architecture offers separate storage and signal buses for instructions and data. This architecture has data storage entirely contained within the CPU, and there is no access to the instruction storage as data. Computers have separate memory areas for program instructions and data using internal data buses, allowing simultaneous access to both instructions and data.Programs needed to be loaded by an operator; the processor could not boot itself. In a Harvard architecture, there is no need to make the two memories share properties.

Von-Neumann Architecture vs Harvard Architecture

The following points distinguish the Von Neumann Architecture from the Harvard Architecture.| Von-Neumann Architecture | Harvard Architecture |

|---|---|

| Single memory to be shared by both code and data. | Separate memories for code and data. |

| Processor needs to fetch code in a separate clock cycle and data in another clock cycle. So it requires two clock cycles. | Single clock cycle is sufficient, as separate buses are used to access code and data. |

| Higher speed, thus less time consuming. | Slower in speed, thus more time-consuming. |

| Simple in design. | Complex in design. |

CISC and RISC

CISC is a Complex Instruction Set Computer. It is a computer that can address a large number of instructions.In the early 1980s, computer designers recommended that computers should use fewer instructions with simple constructs so that they can be executed much faster within the CPU without having to use memory. Such computers are classified as Reduced Instruction Set Computer or RISC.

CISC vs RISC

The following points differentiate a CISC from a RISC −| CISC | RISC | ||

|---|---|---|---|

| Larger set of instructions. Easy to program | Smaller set of Instructions. Difficult to program. | ||

| Simpler design of compiler, considering larger set of instructions. | Complex design of compiler. | ||

| Many addressing modes causing complex instruction formats. | Few addressing modes, fix instruction format. | ||

| Instruction length is variable. | Instruction length varies. | ||

| Higher clock cycles per second. | Low clock cycle per second. | ||

| Emphasis is on hardware. | Emphasis is on software. | ||

| Control unit implements large instruction set using micro-program unit. | Each instruction is to be executed by hardware. | ||

| Slower execution, as instructions are to be read from memory and decoded by the decoder unit. | Faster execution, as each instruction is to be executed by hardware. | ||

| Pipelining is not possible. | Pipelining of instructions is possible, considering single clock cycle. |

No comments:

Post a Comment

commnet here